The discussion around feasible architectures for quantum computers has been largely dominated by superconducting qubits, trapped ions, and neutral atom platforms. Spin qubits, on the other hand, have often been seen as the younger and literally smaller cousin among these options. Despite the promise that spin qubits could leverage materials and technology from the current semiconductor industry, running even NISQ (Noisy Intermediate-Scale Quantum) algorithms on this platform has seemed a distant goal.

However, this future may be gradually materializing. In recent weeks, three manuscripts have presented high-quality qubits fabricated using 300 mm industrial technology, potentially marking the beginning of exponential growth in the number of qubits:

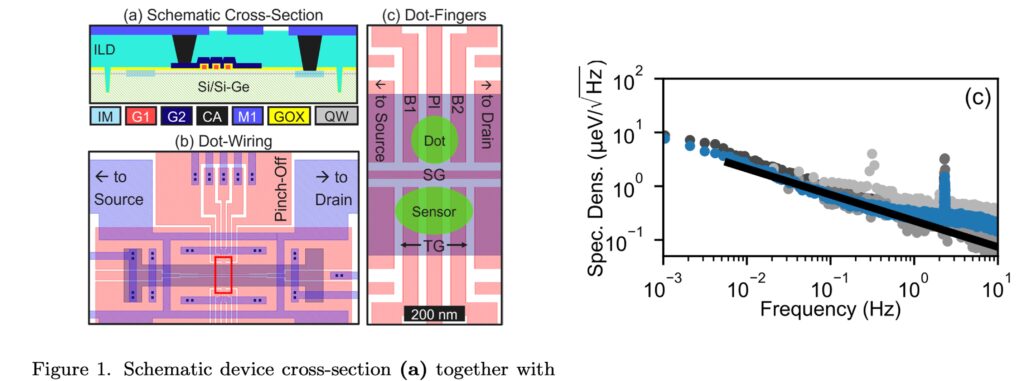

“Altogether, there are more than 24,000 testable quantum dot devices on every wafer (Fig.1c), including 1,230 variations of the 12QD device.”

Before that becomes reality, let’s take a closer look at the current state of affairs.

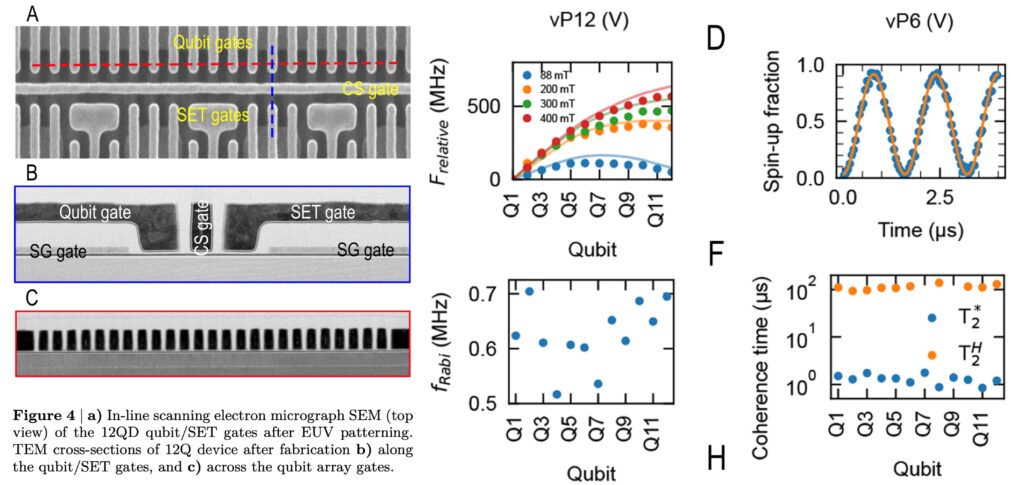

12-Spin-Qubit Arrays Fabricated on a 300 mm Semiconductor Manufacturing Line

The first paper, from Intel, showcases an industrially fabricated 12-qubit array. This work introduces a novel fabrication process, moving away from the academic lift-off method to a more industrial-friendly etching process. After detailing the fabrication methods and the workings of the “Tunnel Falls” test chip, the paper evaluates the performance of the qubits.

The performance isn’t exceptional, but it is impressively uniform. T2* times hover just above 1 µs for all qubits, which is extended by about two orders of magnitude with spin echo applied. This suggests coherence is limited by residual nuclear spins, which are less influential at high frequencies. In addition, the paper demonstrates high tunability of exchange coupling and describes a method for tuning the device.

While this paper represents a potential breakthrough for spin qubit technology, further improvements in both scalability and qubit quality are needed. As it stands, even with well-designed echo pulses (which are challenging to implement during operation), the qubit quality factor is only around 50. This isn’t sufficient for running NISQ algorithms. Still, this performance is on par with state-of-the-art few-qubit devices, which is impressive for the first demonstration of a working 10+ qubit device.

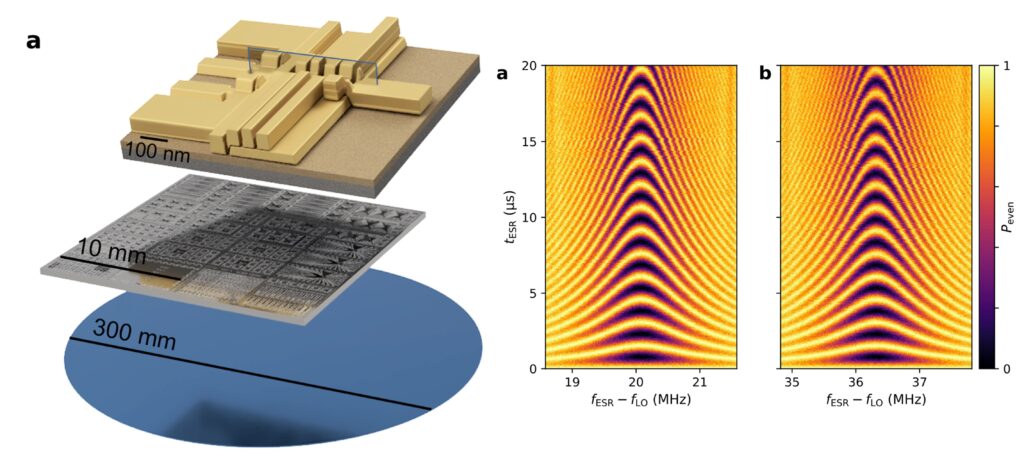

A 300 mm Foundry Silicon Spin Qubit Unit Cell Exceeding 99% Fidelity in All Operations

On the other end of the spectrum, we have proof that high-quality spin qubits are achievable. A second paper, a collaboration between DiraQ and IMEC, presents a two-qubit device fabricated using the same technology as Intel’s 12-qubit array, but with significantly longer coherence times. The highlight of this paper is the record-breaking T2H time of nearly 1 ms, leading to fidelities above 99% for both 1- and 2-qubit operations.

The performance boost seems to stem from a different control method. DiraQ’s device uses ESR (electron spin resonance) with a time-dependent magnetic field, in contrast to Intel’s EDSR (electric dipole spin resonance). ESR doesn’t require the creation of an electric dipole, which makes it less susceptible to noise. However, it remains uncertain whether this approach can be scaled to larger numbers of qubits.

Industrially Fabricated Single-Electron Quantum Dots in Si/SiGe Heterostructures

The third manuscript explores a device fabricated using industrial technology, but with a key difference: Si/SiGe heterostructures replace the SiMOS technology. The paper, from researchers at Aachen, details the device design and offers a basic characterization of charge physics. Notably, the charge noise spectroscopy reveals an exceptionally low charge noise amplitude of 1/f spectrum. At 1 Hz, the noise amplitude is approximately 0.2 µeV/√Hz, a few times lower than that of SiMOS devices. This may allow for electrically driven qubits (as in the first paper) with coherence times comparable to the second.

Summary

Altogether, these papers present important steps toward developing high-quality, practical spin qubit devices. With a clear roadmap visible, one could envision leveraging the best aspects of each approach: long coherence, faster electric control, a 2D grid architecture, multiple arrays, and eventually incorporating coherent spin shuttling between arrays. Crucially, each step can benefit from existing semiconductor technology. Seeing this progress, I am confident that such a device may be just a few years away.